SINTEF A23931- Unrestricted

# Report

# High Temperature Power Electronics Packaging

Reliable packaging technologies for high temperature applications

# Author(s)

Andreas Larsson Torleif Tollefsen, Olav Storstrøm, Truls Fallet

SINTEF ICT

Address: Postboks 124 Blindern NO-0314 Oslo NORWAY

Telephone:+47 73593000 Telefax:+47 22067350

postmottak.IKT@sintef.no www.sintef.no Enterprise /VAT No: NO 948 007 029 MVA

# Report

# **High Temperature Power Electronics Packaging**

**KEYWORDS:**

High temperature, packaging, Silicon carbide (SiC), BJT power transistor, SLID die attach, ceramic substrate, active metal braze (AMB), thermal management

**VERSION**

1.0

DATE

2013-01-17

**AUTHOR(S)**

Andreas Larsson, Torleif Tollefsen, Olav Storstrøm, Truls Fallet

Norwegian research council

CLIENT'S REF.

Øvvind V. Salvesen

PROJECT NO.

191308/\$60

**NUMBER OF PAGES/APPENDICES:**

65 + Appendices

ABSTRACT

# Reliable packaging technologies for high temperature applications

The lack of robust and reliable packaging methods are considered to be one of the main challenges for the next generation of high temperature electronics (>200 °C). Power electronics are especially difficult to operate in this environment. This project investigated packaging technologies suitable for a high temperature power module for operation up to 250 °C. The key technologies investigated were:

- A novel type ceramic substrate active metal brazed (AMB) silicon nitride (Si<sub>3</sub>N<sub>4</sub>) showed no signs of degradation.

- A state-of-the-art Au-Sn solid-liquid interdiffusion (SLID) die attach was developed.

- Silicon carbide reinforced aluminium (AlSiC) with cold sprayed Cu was used as a base

- Different thermal interface materials were investigated.

- Finally, a power module concept was developed. It was based on silicon carbide (SiC) bipolar transistors (BJT).

The main conclusion drawn from this project is that reliable packaging technologies for 200 °C and beyond seem possible. Suitable packaging technologies are emerging but commercially available electronic components compatible with this temperature range and these novel technologies are still very sparse.

PREPARED BY

**Andreas Larsson**

**CHECKED BY**

**Truls Fallet**

APPROVED BY

Ole Christian Bendixen

REPORT NO.

SINTEF A23931

ISBN

978-82-14-04278-8

CLASSIFICATION

Unrestricted

Unrestricted

# **Document history**

VERSION

DATE

VERSION DESCRIPTION

1.0

2013-01-17

First approved version

# Table of contents

| 1 | Sumi  | mary      |                                                                         | 5   |

|---|-------|-----------|-------------------------------------------------------------------------|-----|

| 2 | Intro | duction   |                                                                         | 7   |

| 3 | Subs  | trate te  | chnology                                                                | 9   |

|   | 3.1   | Materi    | ials and methods                                                        | . 9 |

|   |       | 3.1.1     | Silicon nitride active metal brazed, Si <sub>3</sub> N <sub>4</sub> AMB | . 9 |

|   |       | 3.1.2     | Substrate and metallization scheme                                      | 10  |

|   | 3.2   | Results   | s and discussion                                                        | 12  |

| 4 | Back  | side int  | erconnect (die attach technology)                                       | 14  |

|   | 4.1   | Au-Sn     | bonding                                                                 | 15  |

|   |       | 4.1.1     | Materials and methods                                                   | 15  |

|   |       | 4.1.2     | Results and discussion                                                  | 17  |

|   | 4.2   | Au-Ge     | bonding                                                                 | 19  |

|   |       | 4.2.1     | Materials and methods                                                   | 20  |

|   |       | 4.2.2     | Results and discussion                                                  | 20  |

| 5 | Front | side int  | erconnect (wire bonding)                                                | 21  |

|   | 5.1   | Materia   | als and method                                                          | 21  |

|   | 5.2   | Results   | and discussion                                                          | 22  |

| 6 | Encap | sulation  | n                                                                       | 25  |

|   | 6.1   | Confor    | mal coating                                                             | 26  |

|   | 6.2   | Base pl   | ate                                                                     | 26  |

|   |       | 6.2.1     | Materials and methods                                                   | 26  |

|   |       | 6.2.2     | Results and discussion                                                  | 26  |

|   | 6.3   | Electro   | nic liquid                                                              | 27  |

|   |       | 6.3.1     | Results and discussion                                                  | 27  |

| 7 | Thern | nal inter | face materials                                                          | 29  |

|   | 7.1   | High te   | mperature Adhesives                                                     | 29  |

|   |       | 7.1.1     | Materials and Methods                                                   | 29  |

|   |       | 7.1.2     | Results and discussion                                                  | 32  |

|   | 7.2   | Metallio  | c thermal interface materials (TIMs)                                    | 13  |

|   |       | 7.2.1     | Materials and methods                                                   | 13  |

|   |       | 7.2.2     | Results and discussion                                                  | 4   |

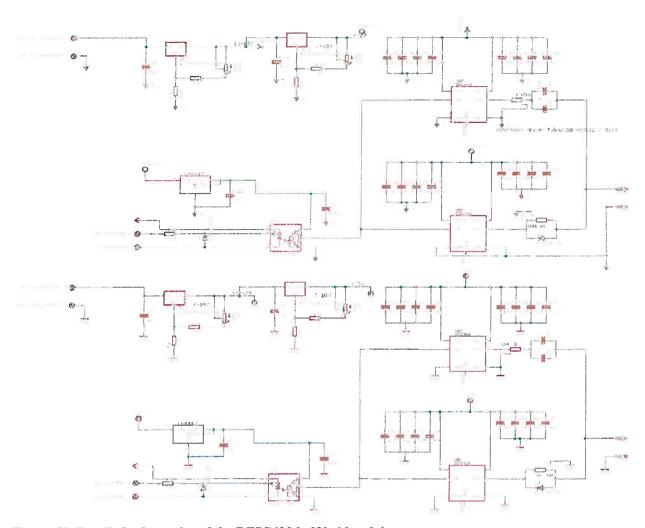

| 8 | Case  | study e | lectronics                                               | .41 |

|---|-------|---------|----------------------------------------------------------|-----|

|   | 8.1   | Silicon | carbide transistors                                      | 41  |

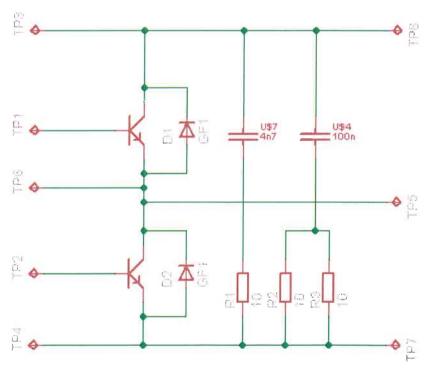

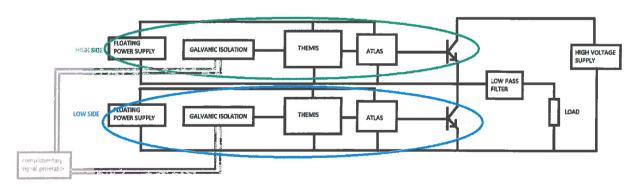

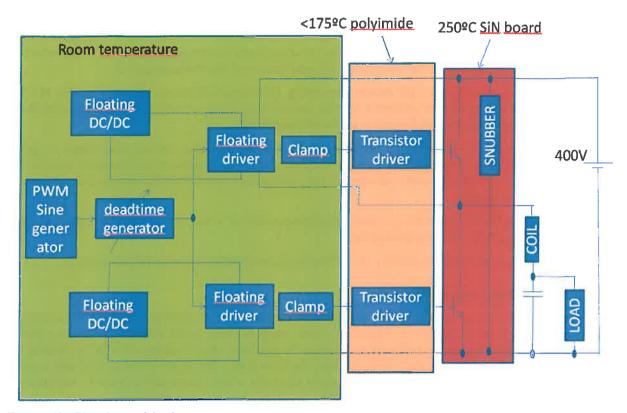

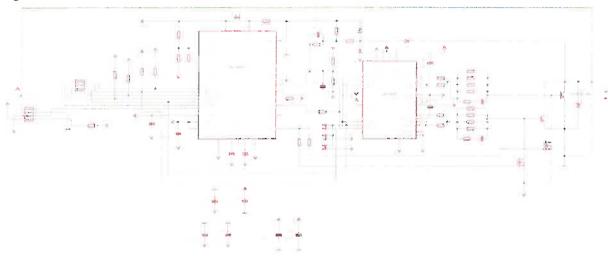

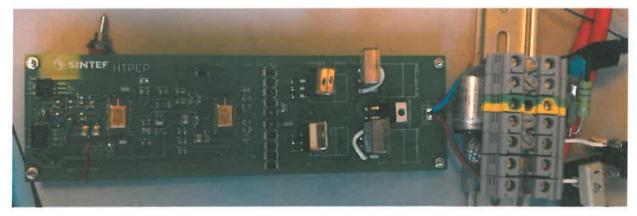

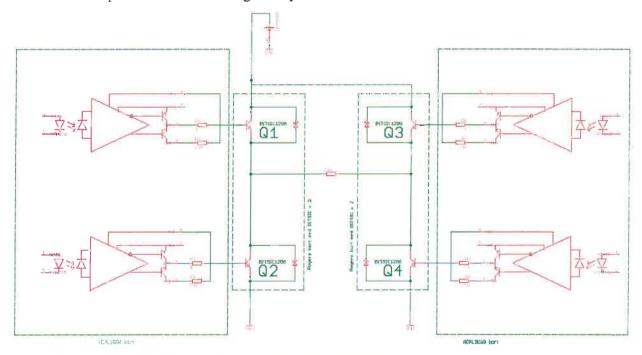

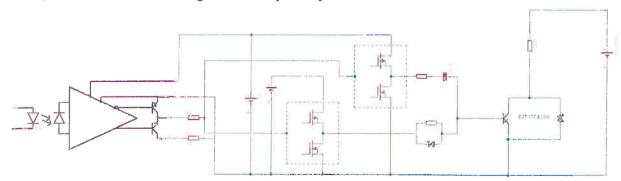

|   | 8.2   | Circuit | topology and partitioning                                | 42  |

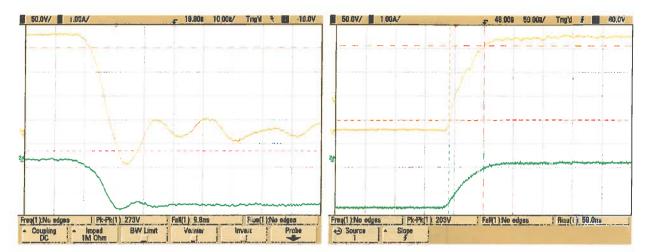

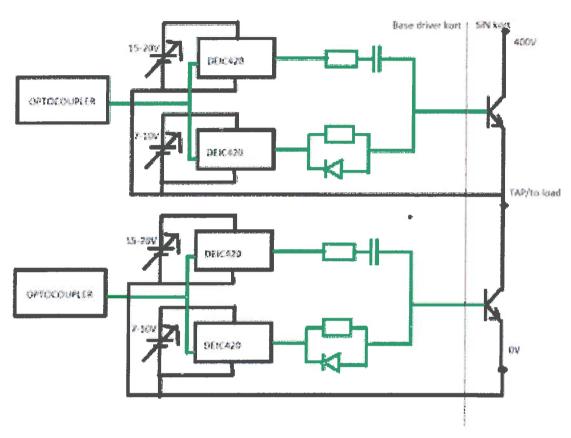

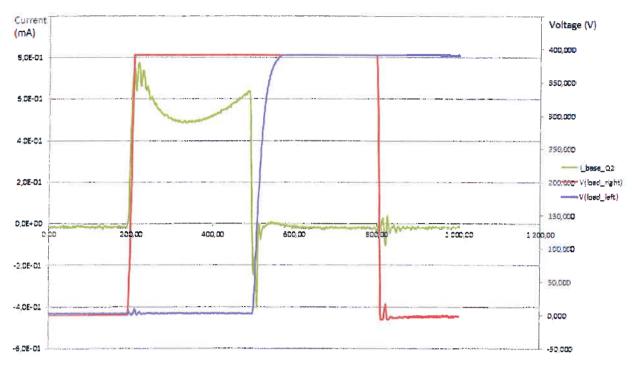

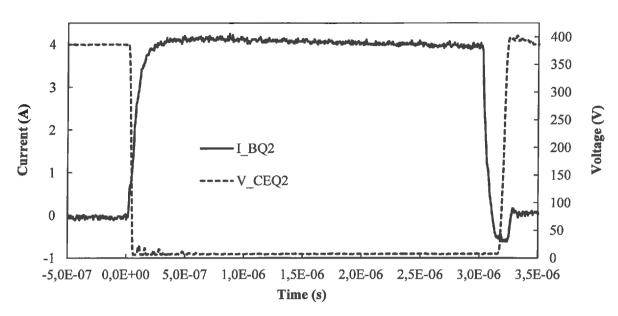

|   | 8.3   | Driving | g a power silicon carbide bipolar transistor             | 43  |

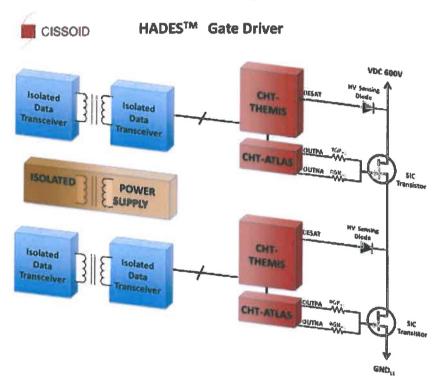

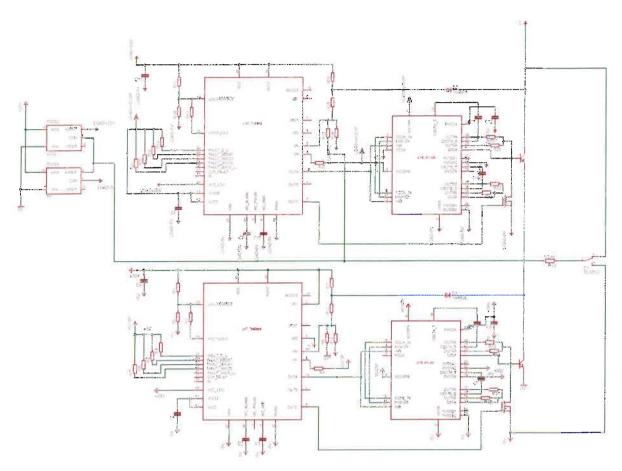

|   |       | 8.3.1   | The CISSOID driver                                       | 43  |

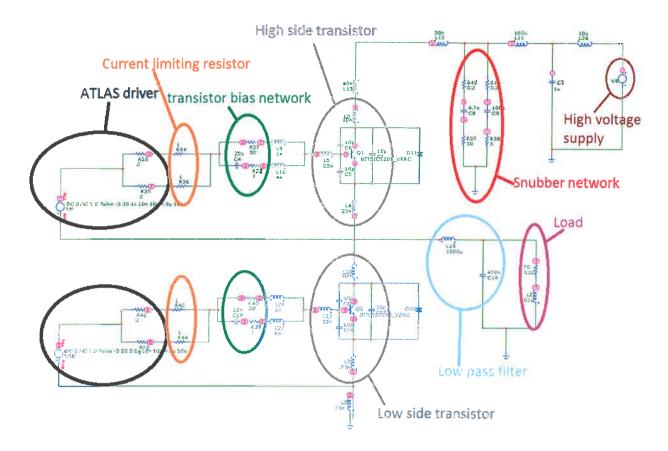

|   |       | 8.3.2   | An alternative driver: IXYS DEIC420                      | 48  |

|   |       | 8.3.3   | Agilent HCPL3000                                         | 51  |

|   |       | 8.3.4   | The final driver using DEIC420 with HCPL3000 optocoupler | 52  |

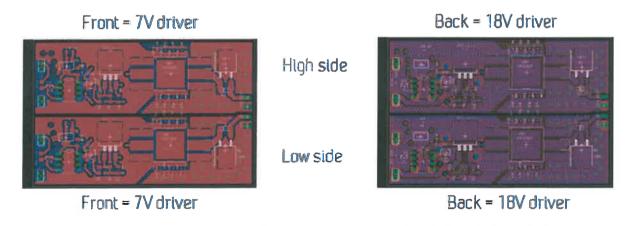

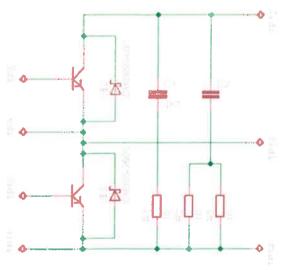

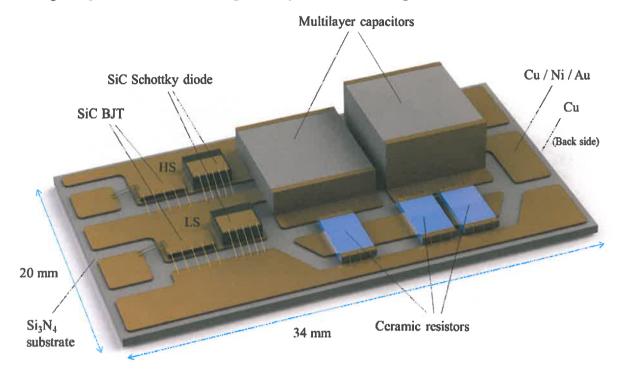

|   | 8.4   | The po  | wer stage circuit board (Power module)                   | 53  |

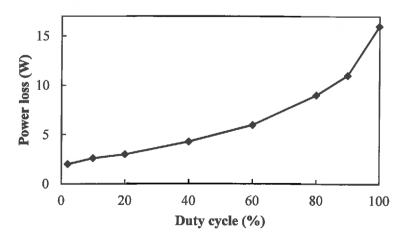

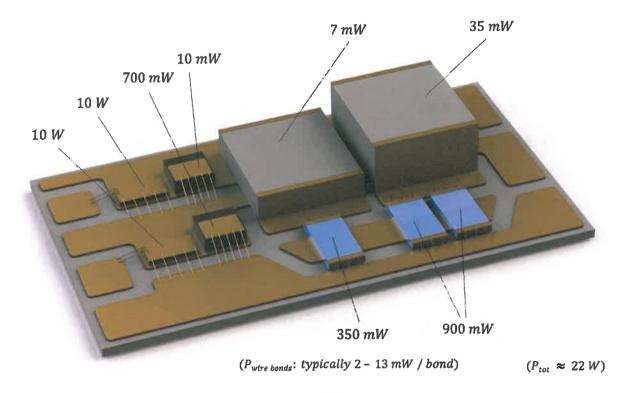

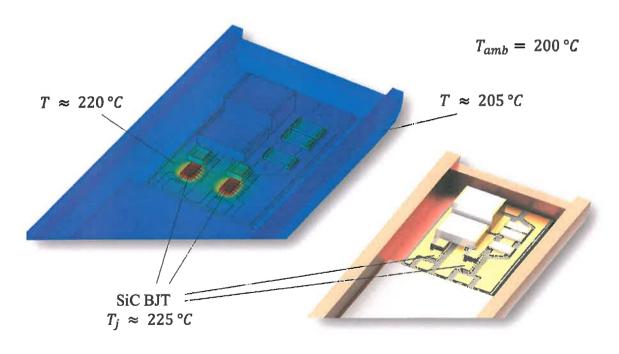

|   |       | 8.4.1   | Power losses and temperature distribution                | 54  |

|   | 8.5   | Compo   | pnents used                                              | 56  |

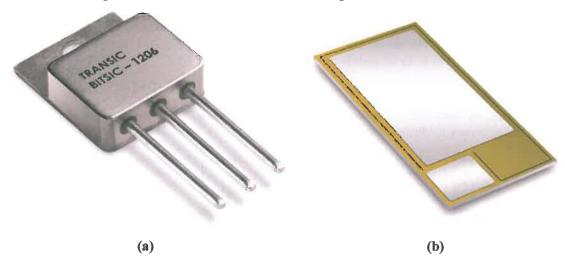

|   |       | 8.5.1   | Transistors                                              | 56  |

|   |       | 8.5.2   | Schottky diodes                                          | 57  |

|   |       | 8.5.3   | Resistors                                                | 57  |

|   |       | 8.5.4   | Capacitors                                               | 57  |

|   |       | 8.5.5   | Substrate                                                | 58  |

|   |       | 8.5.6   | Packaging methods for the components                     | 58  |

| _ |       |         |                                                          |     |

| 9 | Ackno | wledge  | ement                                                    | 59  |

|   | A.1   | Scienti | fic equipment                                            | 60  |

|   | A.2   | Dissert | ation                                                    | 62  |

|   | A.3   | Report  | s and technical notes                                    | 64  |

# **APPENDICES**

A.1 Scientific

A.2 Dissertation

A.3 Reports and technical notes

## 1 Summary

The need for electronics which will operate reliably at high temperature is continuously increasing in the world in general, and especially in the Norwegian oil industry and its associated service companies.

There are mainly two reasons for this:

- The petroleum wells go deeper and the environmental temperature increases

- Several novel drilling- and data collection technologies are based on electrical power

This has led to a need for power control for motors in the kW range operating past 200 °C

There is also a continuous search for new methods in oil exploration. Many of these are based on high temperature electronics. Several of our industrial partners have expressed these reasons for their interest in contributing to the project.

In a greater picture, a strong market pull for high temperature electronics also comes from the aerospace and the automotive industry. Interesting enough, the new "green technologies" like electrical cars and geothermal energy are also in need for electronic power control and very high temperature operations.

Electronic control of high power at high environmental temperatures is a multidisciplinary activity. Just as important as the temperature rating of the individual components is their packaging. Here compactness must be blended with efficient heat transport, mechanical robustness and good electrical performance.

And further on; the properties of the materials used are not limited to strength, heat conductivity and electrical insulation. Their mutual chemical, mechanical and electrical interference is just as important in obtaining a high performance reliable result.

This background is reflected in the objectives and the working methods chosen for the High Temperature Power Electronics Packaging (HTPEP) project.

The primary objective was:

Develop reliable packaging technology for power electronic systems operating at temperatures up to 250 °C.

This was broken down into a number of secondary objectives:

- Develop processes for packaging of SiC and passive components for HT-applications.

- Improve knowledge on failure mechanisms occurring in interconnects and materials used

- Build know-how on SiC component technology

In order to come close to the real world problems that would meet a designer of high power, high temperature electronics, we decided to develop a demonstrator as a part of the project. In cooperation with our industrial partners we chose to make a SiC-power switch for motor control in the kW region.

The main scientific contributions and lessons learned during the project are listed below:

- The foremost achievement for this project was the development of a high temperature (>250 °C) die attach technology; Au-Sn Solid Liquid Inter-Diffusion (SLID) bond process. It has proven to be state-of-art and is by far, as far as the authors know, the most robust and reliable joining technology for harsh applications there is. It was mainly developed within the frame of the PhD study with great synergy and support from the project.

- The emerging ceramic substrate technology based on silicon nitride with active metal brazed (AMB) Cu conductors was shown to be thermo-mechanically robust and a fine match to the silicon carbide (SiC) components for operation up to 250 °C. Plating a patterned substrate with the correct metallization (Cu / Ni / Au) proved to be troublesome, but not restrictive. It will, however, require some effort to develop it into an efficient industrial process.

- Strength evaluation of solid joints must be performed at the operation temperature to provide trustworthy information. This discovery will be provided as a suggestion for improvement of future revisions of international standards, e.g. MIL-STD-883.

- Au wire bonds to Au pads were evaluated and qualified as reliable high temperature interconnects (up to 250 °C).

- Design rules for the application of high temperature compatible ceramic circuit boards were developed.

- Know-how on bipolar junction (BJT) SiC transistors was developed.

- Know-how on feasible high temperature materials such as structural components, thermal interface materials (TIM) and conformal coatings was developed.

## We also experienced that:

- High temperature electronic components, especially capacitors and more advanced circuits (e.g. microcontrollers and memory) are still extremely sparse, limiting the freedom of choice for electrical designs for 250 °C specification. But there is a tremendous R&D activity around the globe nowadays.

- Bare die components with custom made metallization schemes are very hard to get from commercial companies. (I.e. Au based systems instead of the more common and traditional but inadequate Al schemes.) For reliable high temperature system solutions this is crucial.

- To obtain adequate commercial drive circuits for the SiC power switch showed to be much more difficult than anticipated based on available commercial information.

The project generated the following documents and dissertations:

- A PhD thesis to be defended in early 2013

- 1 final project report

- 4 journal articles

- 13 international articles and posters

- 4 international and national popular scientific presentations

- 2 workshops were organized

- 37 part reports and technical notes

- An online database compiling information and datasheets for relevant materials and components were established

The project was started in January 2009 and closed in January 2013. The budget frame for the project was kNOK 8000; kNOK 6400 from the Research Council of Norway and the remaining kNOK 1600 from the project partners. The cost was distributed as shown in Table 1.

Table 1. Projects costs (2012 are budget figures).

| _                                   | 2009 | 2010 | 2011 | 2012 | Sum  |  |

|-------------------------------------|------|------|------|------|------|--|

| Personnel and indirect              | 1180 | 840  | 1550 | 1186 | 4300 |  |

| Purchase of R&D services, incl. PhD | 23   | 580  | 802  | 800  | 2500 |  |

| Equipment                           | 182  | 240  | 22   | 200  | 800  |  |

| Other expenses                      | 105  | 100  | 80   | 100  | 400  |  |

| Total sum                           | 1490 | 1760 | 2464 | 2286 | 8000 |  |

The participating members of the project were:

Badger Explorer, Roxar Flow Measurement (Emerson), TranSiC (Fairchild semiconductor), SmartMotor, Techni, Vestfold University College and SINTEF (coordinator, project manager and main scientific contributor).

#### 2 Introduction

High temperature environments offer great challenges for electronic systems. Although the number of commercially available high temperature components, such as wide band gap semiconductors (e.g. silicon carbide) is rapidly increasing, lack of qualified high temperature packaging technologies limits the growth. In other words: To be able to design and build the next generation high temperature electronic systems, incorporating emerging high temperature components such as silicon carbide, novel packaging methods must be developed.

Silicon carbide (SiC) is a well known material that has long been utilized for its hardness (almost as hard as diamond). This material has only recently has been exploited, in its pure crystalline form, for its semi-conducting properties which e.g. enables low loss high power switching. It is also a stable material at high temperatures which make it ideal for high temperature applications or applications with high power densities. SiC is especially well suited for motor control devices inside hot petroleum wells, where both high energy density (dissipated power) and high ambient temperatures are present.

Motor control systems based on SiC technology provides the means to achieve very high efficiency for electrical motor controllers, which reduce power consumption. But, the main advantage given by SiC technology is the possibility for small low weight solutions. E.g. the automotive industry is adapting SiC technology into emerging electric cars.

To be able to build the next generation of high temperature (>200 °C) compatible power switches with SiC components, other components must be available too. Compatible substrates, capacitors, resistors etc., needs to be identified and specified. All these components must also be prepared for the necessary packaging technologies. I.e. it is crucial that the components have the correct metallization scheme, have a proper surface finish, a suitable thermal expansion coefficient etc.

Perhaps the main challenges to build such a system is the need for novel packaging techniques that is stable and robust at high temperatures. The techniques must produce reliable electrical and thermo-mechanical connections to be useful. This is the main theme of the High Temperature Power Electronics Packaging (HTPEP) project.

Traditionally, oil and gas well drilling has been performed by large oil rigs. With powerful motors that may operate downhole, electronically controlled locally, one may envisage simplified and safer drill operations in the future. SiC technology and adherent novel high temperature packaging technologies will enable this vision.

One of the HTPEP project partners, Badger Explorer ASA, develops a method to drill exploration wells without an open hole to the surface of the seabed. The method requests effective electric motors for the drill. They must be controlled locally by electronics to adapt continuously to the changing environmental conditions during drilling. This novel method for well exploration will both improve safety and reduce the environmental risk. But, it has been characterized as a pioneering technology because will drastically reduce cost framework for future well exploration operations. In addition, the energy consumption for operations will be reduced to about one hundreds of today's level.

Oil and gas technology is essential for the Norwegian society, contributing to more than 50 % of the Norwegian export income and 30 % of the public revenue. The Norwegian petroleum revenue secures the welfare for both todays and coming generations. The development of more efficient oil and gas extraction technologies is therefore important for the Norwegian welfare. Knowledge and technology obtained in this area can also be used in other high temperature applications, such as automotive or aerospace.

The field of high temperature electronics is a broad field, covering many disciplines and markets. Thus, there exist numerous applications for high temperature electronics. By increased monitoring and control of engines used in e.g. automobile and aircraft an optimized combustion and reduced fuel consumption may be achieved. The operation temperature of this electronics is in the range from 300 °C to 600 °C. Extended use of electronics during oil and gas exploration will increase the recovery factor and simultaneously decrease

the risk of emissions to the environment. Downhole electronics can experience temperatures up to 275  $^{\circ}$ C, often in combination with high pressure, vibrations, shock and chemically aggressive ambient media. Other applications for high temperature electronics include space exploration (up to 500  $^{\circ}$ C), geothermal wells ( $^{\sim}$  200-400  $^{\circ}$ C) and nuclear reactors ( $^{\sim}$  200-450  $^{\circ}$ C).

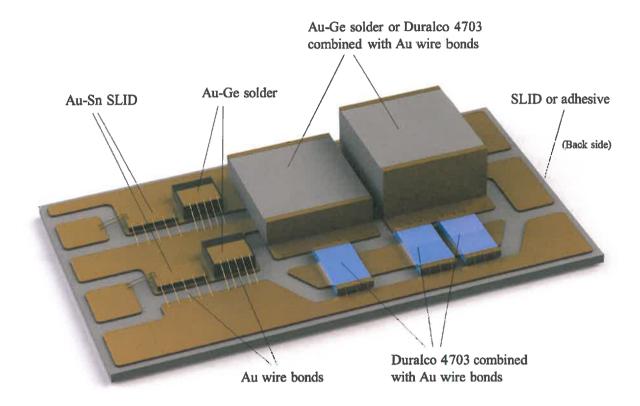

The main objective for the HTPEP project was investigation and development of packaging technologies for high temperature power electronics. The effort was concentrated around an imagined case for a high temperature power module based on SiC technology.

In general, the project found that packaging technologies for operation temperatures beyond 200 °C are emerging. The main results from the project include development of a state-of-the-art die attach technology, joining a SiC device onto a ceramic circuit board. It was tested up to 250 °C and beyond with convincing results. HTPEP was also showed that efficient thermal designs may be developed that will enable higher operation temperatures and/ or longer life times of the electronic systems in the future.

One of the main conclusions drawn from the project was that electronic components for high temperature operation (200 to 250 °C) are still very sparse. Especially as bare die components they seldom have the option of for state-of-the-art high temperature packaging metallization schemes (typically Au based). The large worldwide effort and interest in high temperature electronics that has developed during the project period will certainly assure that the field of high temperature electronics and packaging will advance at a high pace in the time to come.

# Key personnel

The active key members working in the project is presented in Table 2.

Table 2. Key personnel

| Name                     | Title                 | Role                                                                        | Period                                            |

|--------------------------|-----------------------|-----------------------------------------------------------------------------|---------------------------------------------------|

| Andreas Larsson          | Senior scientist      | Project manager (2010-2012)<br>Project participant (2009)                   | Jan 2009 – Jan 2013                               |

| Torleif A. Tollefsen     | Research fellow (PhD) | Task manager – Die attach                                                   | Feb 2010 – Jan 2013<br>PhD ends early 2013        |

| Olav Storstrøm           | Research<br>scientist | Task manager - Electronics                                                  | Jun 2010 – Oct 2012                               |

| Rolf Johannessen         | Research scientist    | Project manager                                                             | Jan 2009 – Jan 2010                               |

| Frøydis Oldervoll        | Senior Scientist      | Project participant (2009) Task manager – Interconnects (Front side) (2011) | Jan 2009 – May 2009<br>and<br>Dec 2010 – Dec 2011 |

| Astrid-Sofie Vardøy      | Master of science     | Project participant                                                         | Jun 2011 – Jan 2012                               |

| Per Schjølberg-Henriksen | Senior Scientist      | Project manager                                                             | Jan 2010 – Feb 2010                               |

# 3 Substrate technology

The substrate is the backbone in electronic systems. It provides the electrical isolation and structural support required to build electronic circuits. And as for all packing components, the mechanical strength and long term robustness is essential for a reliable electronic system. Thus, the requirements for the material properties; mechanical, electrical, thermal etc. are very stringent for any high reliability system.

Hybrid substrate technology is a well proven technology that has been employed for high reliability applications for several decades. It has shown great potential up to 200 °C and beyond. It combines a ceramic core (the board) as the isolation layer with a metal layer on the surface (the conductors); traditionally with thick and thin film technologies and low and high temperature co-fired ceramics (LTCC and HTCC). Several approaches have been explored to improve the performance, especially for improved thermal cycling capability, of the ceramic/metal technology including; direct bonded metal, typically Cu or Al (DBC and DBA) as the most common high reliability technologies today. Still, mechanical failures occur frequently when exposed to elevated temperatures for longer time periods. Typical failures are delamination of traces from the surface (adhesive failure) and cracking of the ceramics itself (cohesive failure). This is primarily due to great stress induced in the system by a large mismatch in coefficient of thermal expansion (CTE) between materials. Typically, the CTE for metals are in the region 15–30 ppm/K and for ceramics it is around 3–10ppm/K. Locally, the mismatch can get even more severe by discrete components assembled on the substrate (SiC and Si with a CTE in the region 2–4.5 ppm/K).

In recent years a novel technology, active metal brazed (AMB) ceramics, has appeared with promising adhesive and cohesive properties based on a strong ceramic core. The most common material for the traces are noble metals; Au, Ag and Cu. The core is typically made of silicon nitride or aluminium nitride. This technology is promising and feasible for future high temperature applications.

Another interesting technology worth mentioning is  $\mu$ -DBC that emerged during the project. It is similar to the standard DBC technology, but the metallization thickness is thinner, < 50  $\mu$ m, than for normal DBC. This makes it more compliant to thermo-mechanical loads, i.e. generates lower stress, than standard DBC substrates. It has shown promising high temperature cycling results compared to DBC [De Langlade ATW 2011]. Compared to AMB substrates it might offer improved design rules, e.g. allowing a finer pitch. Since, the chosen substrate, silicon nitride AMB, showed excellent results throughout the project,  $\mu$ -DCB was never investigated further but might be explored in future projects.

### 3.1 Materials and methods

### 3.1.1 Silicon nitride active metal brazed, Si<sub>3</sub>N<sub>4</sub> AMB

The substrate technology chosen for the HTPEP project was a silicon nitride, Si<sub>3</sub>N<sub>4</sub>, with active metal brazed conductors.

Si<sub>3</sub>N<sub>4</sub> is low to medium cost ceramic substrate material commonly used when high mechanical strength (~900 MPa in flexural strength) combined with high thermal conductivity (90 W/mK at room temperature) is requested. It has a matching CTE; ~3.5 ppm/K, to SiC, Si and ceramic components. The substrate has shown great thermal cycling capability surpassing all other competing technologies, Al DBC, Si<sub>3</sub>N<sub>4</sub> DBC, Alumina LTCC etc. The high thermal conductivity combined with substrates as thin as 300 μm provides excellent thermal properties with a low effective thermal resistance; typically in the magnitude order of 10 mm<sup>2</sup>K/W. The substrate may be produced with both Au and Cu conductors, but the Cu alternative is more readily available.

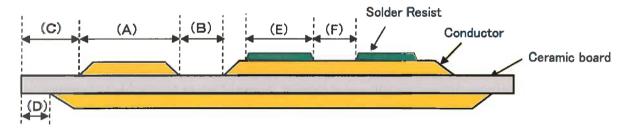

The active metal braze technology may be described by that a sheet of metal is brazed with a solder onto the ceramic core at a process temperature around 600-800 °C creating strong adhesion between the metal and ceramic. The substrate is typically thermally balanced with a symmetric pattern on the back side to minimize warpage and reduce residual stress from the fabrication process. Due to the design rules, this back side

pattern may not always be a perfectly symmetric design, i.e. including mirrored traces. Denka was one of the first suppliers of Si<sub>3</sub>N<sub>4</sub> AMB substrates and holds several patents on the technology. Competing companies, Kyocera and Rogers (curamik), has developed their own technology offering similar products as Denka (they are also referred to as AMB ceramics). In addition to the Denka substrate, they now offer other interesting and attractive options as well, such as finer pitch and multi layer structures. This could be interesting for future applications.

#### 3.1.2 Substrate and metallization scheme

The investigated substrate was delivered by Denka chemical. Kyocera was also contacted to supply substrates for evaluation, but we were unable to attain any samples. The metallization for the substrate was based on a traditional ENIG process (Ni plating with immersion Au) on the Cu surface. Additional thickness of the top Au layer was added to prepare for the Au-Sn SLID process, described further in section 4.

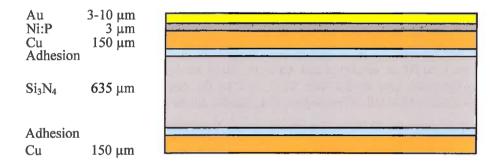

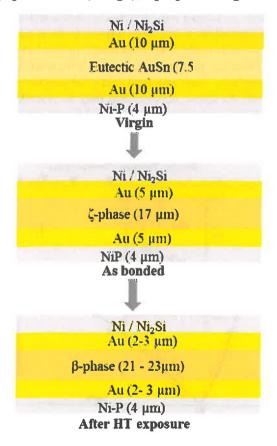

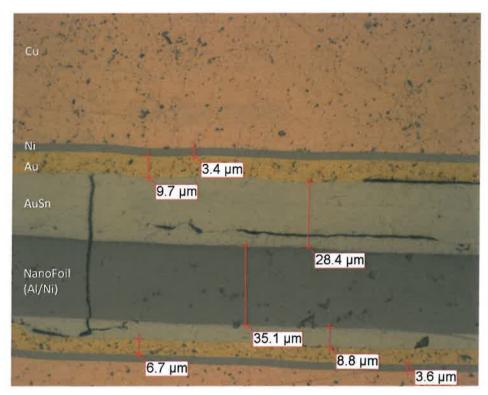

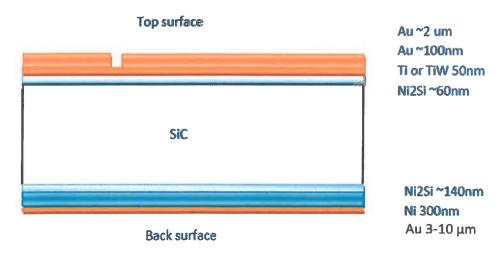

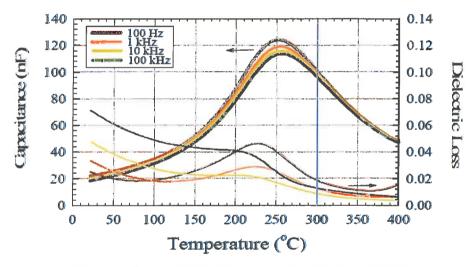

Dummy substrate — The investigated substrate metallization system is shown in Figure 1. The layer functionality is presented in Table 3.

Figure 1. Substrate metallization scheme.

Table 3. Functionality of the individual layers in the substrate stack in Figure 1.

| Layer                          | Functionality                                                                                         | Comment                                                                                                                                                                 |

|--------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Au                             | Bondable surface Compliant (mechanical absorption) Diffusion barrier between Au and Sn Anti-oxidation | This is further explained in section 4.                                                                                                                                 |

| Ni:P                           | Diffusion barrier between Cu and Au                                                                   | 7wt%P                                                                                                                                                                   |

| Cu                             | Circuit layer Thermal balance                                                                         | Front side (top)  Back side (bottom)                                                                                                                                    |

| Adhesion                       | Adhesion to ceramic                                                                                   | Propriety material. Patent [US 2009/0283307 A1] states that Ag and Cu and an active metal are used. Active metals include; Ti, Zr, Hf, Nb, Ta, V and compounds thereof. |

| Si <sub>3</sub> N <sub>4</sub> | Structural Electrical isolation                                                                       |                                                                                                                                                                         |

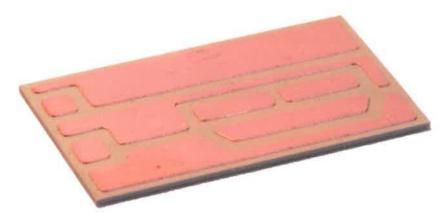

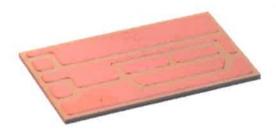

Final substrate – The final circuit board (Figure 2), designed for the case study, had the same structure as the dummy substrate but was ordered without the Ni layer because it was not possible to get Ni only on the front side of the substrate. The possibility for a Cu / thermal interface material (TIM) / Cu joint between the

substrate and base plate requested the back side surface was to have bare Cu. This option was attractive for two reasons; first the chosen TIM would only have been compatible with one surface material and secondly there exists several adhesives suitable to bond to Cu.

Electro-plating was planned to build the required Ni and Au layers. The electro-plating process was unfortunately never attempted since we never found a practical way to manage this. Several methods were tried.

Au wire bonds to the Cu surface were tried to electrically connect the isolated traces on the surface to prepare the substrate for electro-plating. It gave too low yield with unreliable bonds.

Ti has shown to be a suitable diffusion barrier between Au and Cu for HT applications. Thus it is feasible to replace the Ni with a Ti layer. At least 100 nm Ti is required for the barrier. 200 nm Ti and 200 nm Au was applied with chemical vapour deposition (CVD) on the Cu surface. CVD does not require electrical connection between the traces. A simple peel test using regular office Scotch tape was used for a first inspection. The results were unsatisfactory with poor adhesion of the Ti to the Cu surface. This may either come from possible residual stress or perhaps from adhesive residues from the masking tape (Kapton). Ti is known from the Si industry to easily create high residual stress in the interface unless the process is optimized.

An attempt to deposit 1  $\mu$ m Ni followed by 200 nm Au by chemical vapour deposition (CVD) was initiated. The traces covered with the 200 nm Au layer should have been interconnected with Au wire bonds to prepare the subseries for the final 10  $\mu$ m electro-plated Au layer. Au to Au wire bonds is a standard process which should not be any problem. Due to the high work load of the operator of the CVD equipment combined with the short amount of time left of the project, this process was never investigated.

Another alternative was also proposed to solve the plating issue. Cambridge University in the UK was contacted, since they have equipment and experience to deposit similar metals, and they were positive to have a go at it, but unfortunately there was neither time nor resources to follow this path before the project end.

Alternative approaches, such as, custom made structures with spring loaded pins to create electrical interconnection between the traces to prepare the samples for electro-plating were suggested but never realized.

Chemical plating was another option, but it is uncertain if the required thickness of the layers is feasible to build by this method.

Figure 2. Fabricated substrate for the case study. Without the Ni / Au top layers.

Figure 3. Micrograph of the surface of the final substrate with CVD deposited Ti and Au after a peel test. The exposed Cu surface beneath the Au /Ti layer is clearly visible.

#### 3.2 Results and discussion

Simulations

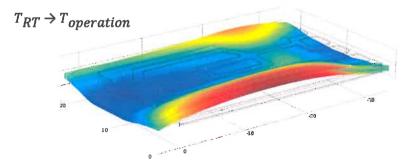

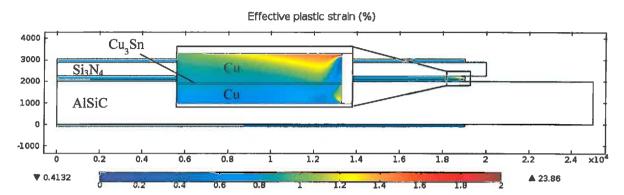

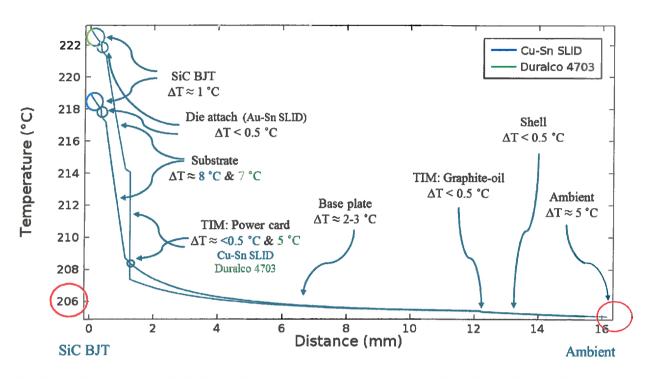

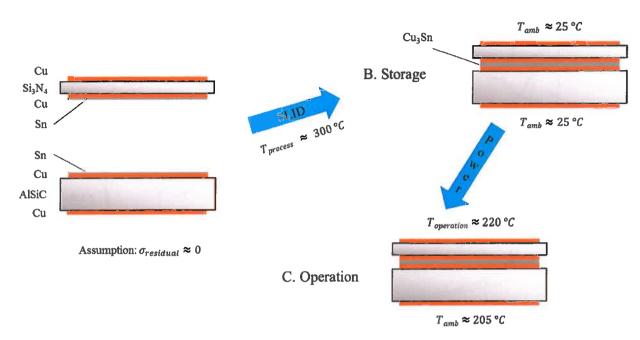

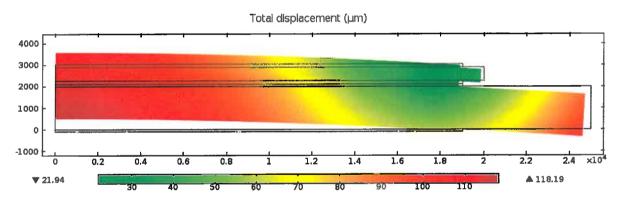

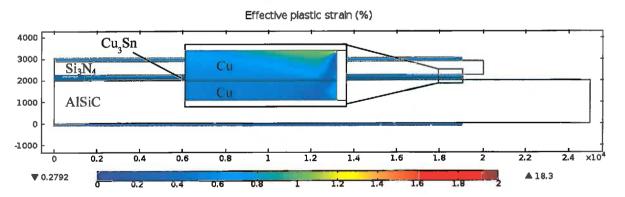

The final substrate design of the circuit board for the case study was investigated by finite element analysis performed in COMSOL Multiphysics. The substrate was assumed to have a strain reference temperature at room temperature (RT). An initial analysis, A, showed potential warpage of the substrate when exposed to operation temperature,  $T_{operation}$  (Figure 4). The thermo-mechanical stress inside the substrate was also analysed for a possible case, B, when the substrate was exposed to a bond process temperature,  $T_{process}$ , of 300 °C, securing the substrate to a AlSiC base plated with a Cu-Sn SLID bond and then taken back to room temperature,  $T_{RT}$ . A third case, C, investigated the thermo-mechanical stress during operation,  $T_{operation}$ , at 220 °C for the same Si<sub>3</sub>N<sub>4</sub> / Cu-Sn / AlSiC system. The analysis showed that the substrate was tending to bend and warp due to the mismatch in coefficient of thermal expansion (CTE) within the system. I.e. the additional stress inside the joints from the warpage in a final system may reduce the system life time or in worst case cause catastrophic mechanical failure in the interconnects. The warpage also resulted in high plastic strain, ~ 20 %, inside the Cu layers (Figure 5). This is in the region of to the maximum elongation at break for Cu; 10-50 % depending on process and material quality. This indicates that there might be a cohesive fracture at the corners of the Cu traces on the substrate. Adhesive failure inside the adhesion layer between the Cu traces and ceramic core also seems possible. Additional information of the analysis of case B and C may be found in [Larsson HiTEC 2012] and in section 6.

Figure 4. Potential warpage at operation temperature assuming strain reference temperature at room temperature (RT) for case A. The deformation in the figure is amplified by a factor of 100. The maximum peak-to-peak deformation was up to 40 μm.

Figure 5. Effective plastic strain inside the metal layers at room temperature after a Cu-Sn SLID bond process (case B). The effective plastic deformation may reach up to  $\sim$ 20 %.

# Experiments

Dummy substrate — The die attach, metallization scheme and substrate are closely coupled in realistic applications. Therefore, the substrate was mainly investigated by experiments in the configuration shown in Figure 8. The stack was exposed to 1000 thermal cycles between 0 to 200 °C, stored at 250 °C for up to 6 month and stored at 250 °C for 3 month followed by 1000 thermal cycles between 0 to 200 °C. Not a single substrate of the more than 100 tested samples that were exposed to the thermal aging tests showed any sign of degradation or failure.

Final substrate – The final substrate (without Ni and Au) was attached with an adhesive to an AlSiC base plate and stored at 250 °C for 2700 hours without any signs of delamination or cracking or any other failures. More information about this experiment is found in section 7.

The simulations suggested that there might be cracks at the corners. No such cracks were found for the real substrates exposed to 250 °C for 2700 hours. A visual inspection by optical microscopy for these cracks was performed.

# 4 Back side interconnect (die attach technology)

The choice of interconnect technology, i.e. the conductive path required to achieve connection from a circuit element to the rest of the circuit, is of utmost importance in electronic devices. Commonly used interconnect techniques include solders, welding and conductive adhesives. However, for high temperature (HT) applications, the standard interconnect materials do not meet the requirements regarding e.g. high temperature stability. There is a limited range of high temperature interconnect techniques. One alternative is sintered nano-particle Ag, which has good electrical and thermal conductivity. A nano-particle Ag joint has a high melting point (960 °C) compared to the low processing temperature (< 300 °C). However, Ag migration is reported to be a problem in high temperature applications (particularly in combination with high power) combined with a non uniform joint with pores, limiting the lifetime of the joint. Another interconnect, solder type, that has shown interesting high temperature results is eutechtic Au-Ge which melts at 361 °C and therefore is a potential high temperature candidate for operation above 200 °C.

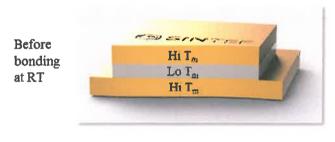

Other prospective high temperature interconnect techniques include liquid-based solder joints, composite solder joints, bismuth-based solder joints, and solid-liquid interdiffusion (SLID) joints. Of these techniques, SLID bonding – also called Transient Liquid Phase (TLP) bonding, isothermal solidification, or off-eutectic bonding – has shown great potential. The SLID technique uses a binary system consisting of two metals with different melting points  $T_{\text{low}}$  and  $T_{\text{high}}$ , and relies on the formation of intermetallic compounds (IMC). At a processing temperature above  $T_{\text{low}}$ , IMCs will form. They will have a higher melting point than  $T_{\text{low}}$ , giving bonds that are stable above the processing temperature. The general principles of the SLID bonding process are illustrated in Figure 6.

Thin low T<sub>m</sub> interlayer sandwished between high T<sub>m</sub> joint parts

Melting of low T<sub>m</sub> interlayer and interdiffusion

Homogeneous joint / IMC formation where solidification is isothermal

Figure 6. Schematic illustration of solid-liquid interdiffusion (SLID) bonding ( $T_B$ : Bonding temperature,  $T_m$ : Melting temperature, RT: Room temperature, IMC: Intermetallic compound).

# 4.1 Au-Sn bonding

SLID bonding has been performed in various metal systems. Examples include Ag-In, Ag-Sn, Au-In, Au-Sn, Cu-Sn and Ni-Sn. Ag-In, which is among the first SLID systems, has been investigated for high temperature applications in several studies. Here, a high temperature stable joint can be achieved (stable up to 700 °C) using a processing temperature of only 210 °C, followed by annealing at 150 °C. However, the high temperature lifetime of the joint is reported to be limited (especially in combination with high power), due to Ag migration.

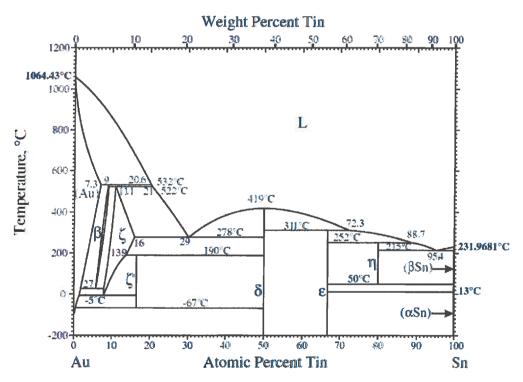

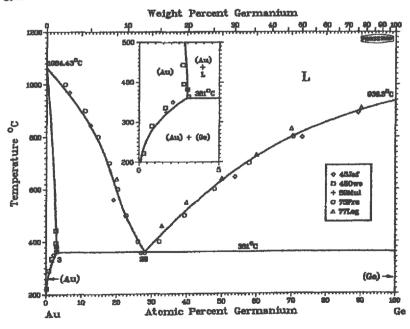

Au-Sn is a promising SLID system for high temperature applications. Based on the Au-Sn phase diagram (shown in Figure 7), several Au-Sn phases can be appropriate for high temperature applications. However, when long time stability is taken into account, the  $\zeta$  phase is the most promising. The final bond structure was reported to be layered – Au /  $\zeta$ ' / Au – where the  $\zeta$ ' phase undergoes a phase transition to the  $\zeta$  phase at 190 °C. The  $\zeta$  phase has a melting point of 522 °C, making it desirable for high temperature applications. Thorough investigations of the Au-Sn phase diagram suggests that the actual layered bond structure probably is Au /  $\zeta$  / Au, since the  $\zeta$  phase is stable down to -5° C (depending on Au concentration). Another possible bond structure is Au /  $\beta$  / Au. The  $\beta$  phase has an even higher melting point than the  $\zeta$  phase, i.e. 532 °C. However, the  $\zeta$  phase is reported to be tougher (more fracture resistant) than the  $\beta$  phase, indicating that a Au /  $\zeta$  / Au bond probably is more reliable than a Au /  $\beta$  / Au bond. Au-Sn SLID has already shown good high temperature stability and thermal cycling abilities in studies performed by Johnson *et al*.

Figure 7. The Au-Sn phase diagram.

#### 4.1.1 Materials and methods

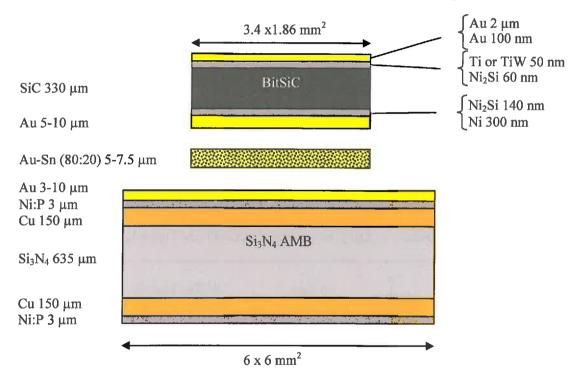

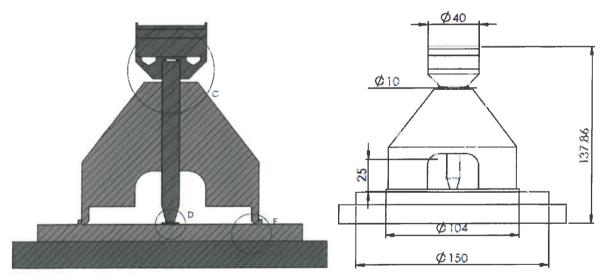

The material stack for the die / die attach / substrate is shown in Figure 8.  $Si_3N_4$  substrates with active metal bonded (AMB) Cu (150  $\mu$ m) and plated Ni-P (7wt%P) were used as substrates for all SLID samples. The substrates had symmetrical metallization (Cu / Ni-P layers on both top and back side) to minimize warpage of the substrate due to coefficient of thermal expansion (CTE) mismatches between  $Si_3N_4$  and Cu. An additional Au layer (3 to 10  $\mu$ m) was electroplated on the substrates in a gold cyanide solution at a

temperature range of 60-65 °C, with a current density of 2.7 mA/cm<sup>2</sup>. The substrate was diced in 6x6 mm<sup>2</sup> samples after plating.

The BJT SiC dummy chips, delivered from Fairchild, had a sputtered Ni<sub>2</sub>Si / Ni / Au metallization (cf. Figure 8). The chips were electroplated with a uniform Au layer (5 to 10  $\mu$ m), and diced in 1.855 x 3.4 mm<sup>2</sup> samples.

Assembly was performed in two steps; first, the substrate, the eutectic Au-Sn preform (80:20 wt%) and the chip were aligned manually on a hot plate and fastened with a clamping force corresponding to 2.5 MPa on the surfaces to be bonded. Secondly, the samples were bonded using a hotplate. Bonding was performed in a vacuum chamber (chamber pressure 10 kPa / 75 torr). The samples were heated to 250 °C and held there for 5 min (to bake out any residual moisture and to assure a uniform temperature distribution in the bonding layers). Then, the samples were heated to 350 °C, and kept there for 5-20 min to ensure that the desired phases were created

Die shear testing is a technique to determine the integrity of materials and methods used to attach semiconductor die or surface mounted passive elements to substrates. It is among the most commonly utilized bond strength characterization methods. The method is effective regarding cost and time.

Figure 8. Investigated stack with a dummy SiC component on the top attached to the  $Si_3N_4$  AMB substrate with the Au-Sn SLID bond.

The subjected samples were exposed for different environmental tests to investigate their reliability. High temperature storage (HTS), a test to examine the reliability of the subjected packages at specified conditions over an extended time period, was performed at 250 °C in air for 1, 3, and 6 months. This test is very important for high temperature packages, since high temperature environments will accelerate intermetallic diffusion and creep mechanisms. This can result in the formation of new brittle intermetallic compounds (IMCs), Kirkendall voids (the formation of voids due to a difference in diffusion rates), or void and/or crack formation generated from creep, which all will reduce the reliability of the subjected package.

Thermal cycling (TC), a test to determine the resistance of the package at extremes of high and low temperatures, and the effect of alternate exposures to these extremes, was performed. The test exposes the package to mechanical fatigue induced by coefficient of thermal expansion (CTE) mismatches in the package. Important parameters besides the temperature extremes include the dwell time and the transfer time between temperature extremes. It is important that both the dwell and transfer time is long enough to ensure approximate structural equilibrium in the materials in the subjected package. Thermal cycling was performed on selected samples between  $0-200\,^{\circ}$ C, with a gradient of  $10\,^{\circ}$ C/min, and a dwell time of  $15\,^{\circ}$ min at the temperature extremes.

A combination of HTS and TC was also performed. If a package is intended for an application experiencing both high temperature and temperature variations, it will be important to test the same samples for both storage and cycling. Storage can induce a phase transformation in the die attach and interconnection materials. It is therefore important to verify that stored samples also can withstand the mechanical fatigue introduced during thermal cycling afterwards.

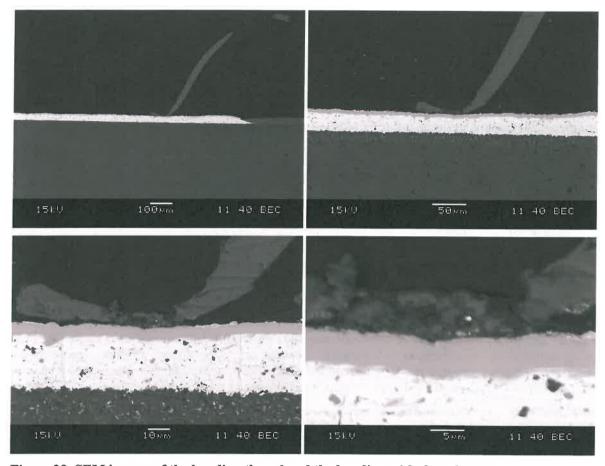

#### 4.1.2 Results and discussion

It has been demonstrated that Au-Sn SLID bonding is an excellent die attach and interconnect technology for high temperature applications. It has also been shown that Au-Sn SLID can withstand large temperature variations in a packaging system with large residual thermo-mechanical stress (induced by CTE mismatches). Other technical contributions include:

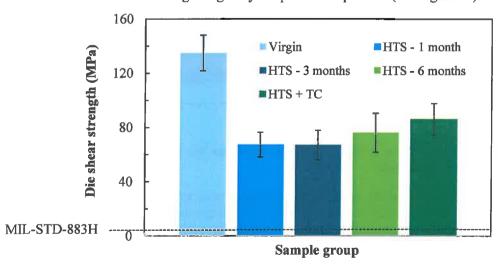

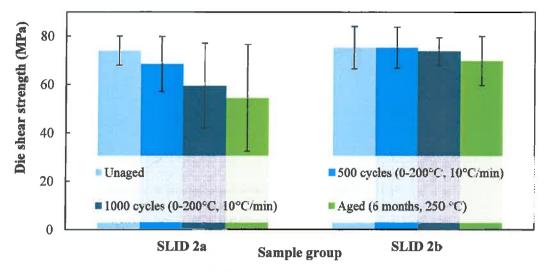

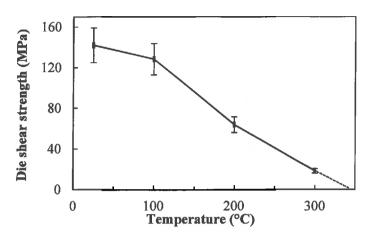

- Demonstrated high shear strength, about 70 MPa, after high temperature exposure at 250 °C and after cycling between 0-200 °C (see Figure 9).

- Demonstration of the importance of a symmetric Au-Sn SLID bond, and excess Au (compliant layer) on both chip and substrate (see Figure 9).

- Optimization of bonding parameters (temperature 300 °C, total bonding time (above eutectic melting point) 6 min), and demonstration of the importance of conducting the bonding in absence of O<sub>2</sub>.

- Optimization of the geometry / thickness of the Au and Au-Sn layers in a SiC / Ni / Au / Au-Sn / Au / Ni / Cu / Si<sub>3</sub>N<sub>4</sub> package regarding thermo-mechanically stresses induced by CTE mismatches.

- Shown how the bond configuration of a Au-Sn SLID bond changes at different stages during high temperature exposure, from the  $\zeta$ -phase to the  $\beta$ -phase (see Figure 11).

- Shown that the shear strength is greatly temperature dependent (see Figure 12).

Figure 9. The shear strength of the optimized Au-Sn SLID samples (Virgin) after and thermal ageing  $(1, 3 \text{ and } 6 \text{ months at } 250 \,^{\circ}\text{C})$  and a combination of thermal aging (HTS) and cycling thermal cycles (TC)  $(0-200\,^{\circ}\text{C}, 10\,^{\circ}\text{C/min})$ , dwell time of 15 min).

Figure 10. The shear strength of Au-Sn SLID samples as a function of the number of thermal cycles (0 -200 °C, 10 °C/min, dwell time of 15 min) and thermal ageing (6 months at 250 °C). Note that this figure is only included to visualize the main trends. Since many of the tested samples did not fracture during testing, due to the equipment limit (50 kgF), a proper average cannot be made.

Figure 11. A schematic overview of the layered structure of an optimized Au-Sn SLID bond at different life stages. The different material phases were identified with energy dispersive spectroscopy (EDS) and x-ray diffraction (XRD).

Figure 12. The average shear strength of Au-Sn SLID samples as a function of temperature. Each point is based on six measured samples. The dotted line represents an extrapolation of the line to indicate the effective melting point of the bond.

# 4.2 Au-Ge bonding

Eutectic Au-Ge (88:12 wt%) has an eutectic melting point at 361 °C which makes it possible to use for high temperature applications above 200 °C. Unlike Au-Sn it has no stable phases to higher temperatures than the eutectic point (see Figure 13). Nonetheless it has been shown to be a reliable die attach material at high temperatures. Banu *et al.* showed that it could withstand tough thermal cycling (4000 cycles between -170 °C to 270 °C with 40 °C/min) without any failures as a die attach for a SiC Schottky diode (of similar size as the dummy BJT chip) to a BeO substrate. They also qualified it for junction temperatures above 300 °C. This makes it a suitable high temperature die attach material that may be reworked and used on components with thin Au layers (less than a couple of  $\mu$ m) where Au-Sn solid-liquid interdiffusion (SLID) will not work. Unfortunately, thick Au layers (> 1  $\mu$ m) on components are sparse today. This may limit the potential use of the SLID technology.

Figure 13. The Au-Ge phase diagram.

#### 4.2.1 Materials and methods

The same test system was used as for the Au-Ge bond as for the Au-Sn SLID bond, only with a 25  $\mu$ m thick and 1 mm wide eutectic Au-Ge foil instead of the Au-Sn preform (cf. Figure 8). The bonding was performed on a desktop hotplate in a regular lab (Figure 14). It was performed in a  $N_2$  atmosphere to avoid  $O_2$  contaminating of the surfaces, prior and during bonding. The bonding was performed at process temperatures at around 450 °C. The bond process was never optimized.

Figure 14. Photograph of the setup during bonding of a Au-Ge test sample (initial bonding in progress).

### 4.2.2 Results and discussion

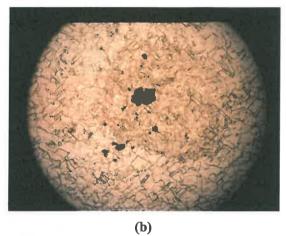

The bonds created were as strong as suggested by the literature, around 50-60 MPa, thus the process was believed to be good enough. The typical fracture surface seemed to be in the Ni<sub>2</sub>Si layer on the SiC dummy chip which was odd since this was not observed for the Au-Sn SLID samples. Perhaps it was due to the high process temperature? It was hard to tell whether the fracture was adhesive or cohesive. A typical fracture surface is shown in Figure 15.

Figure 15. Micrograph of the fracture surface for a sample bonded with eutectic Au-Ge.

# 5 Front side interconnect (wire bonding)

The most common wire bond materials are Au and Al. Both Au and Al have shown interesting results for high temperature applications, but the combination of Au and Al creates a weak brittle phase: AuAl<sub>2</sub> often called purple plague. One advantage of using Al instead of Au is that larger wire diameters of the Al wire are available compared to Au wires, hundreds of µm compared to tens of µm. This reduces the current density inside the wires for an equivalent current, i.e. inhibiting electromigration. But combining Al wires with a Au top metallization requires a diffusion barrier between Al and Au. Ni is a well known high temperature barrier between Al and Au. One the other hand, since the substrate surface is Au and the other components also have Au metallization on the terminations/ pads, the monometallic Au system seems far more attractive and much more predictive. In addition, Au suffer less from electromigration than Al. Johnson et al. have shown that Au to Au wire bonds may provide reliable and high strength bonds for high temperature applications. After 10000 hours at 300 °C the bonds still managed from 5 g pull force (MIL-STD-883H states that 2.4 g is accepted for the Ø25 µm Au wires used by Johnson et al.). Limited Au-Au diffusion at the interface has been observed. Estimation showed that a minimum of five Ø50 µm Au wires should be enough for the case study (I<sub>c</sub> < 10 A per transistor) to avoid significant local joule heating, keeping the local over-temperature ( $\Delta T \approx 30$ °C) of the wires at bay, as well as securing a comfortably low current density (<1 MA/cm<sup>2</sup>) to minimize electromigration. (Typically, current densities >1 MA/cm<sup>2</sup> at 300 °C for time periods of month are used to perform accelerated tests on electromigration.)

Another interesting variant of wire bonding are ribbon bonding which is very similar. A foil with a rectangular cross-section is thermo-compression bonded to the surface instead of wires. This provides a way to get large cross-sections of pure Au interconnect system, reducing the current density, i.e. avoiding possible electromigration issues. Au wire bonding is far more common and readily available than Au ribbon bonding.

Worth mentioning also is that Cu wire bonds have been given much attention in recent years, opening for a possible pure Cu system in the future. This system is still under development for normal temperature applications.

# 5.1 Materials and method

Al metallization are the typical contact metal on common components (most often without Au as an option). It was also believed that Al wire bonds were required for the CISSOD bare die chipset (they had most likely Al as top metallization, cf. section 8). As mentioned in the pervious section, Au wire bonds to Au pads had been investigated with good results for high temperature applications already. Therefore, Al wire bonds were chosen for investigation. The alumina test substrate was alumina with silver thick film (Heraeus C8717B) and cover varnish (Heraeus GPA 200900). The silver metallization was plated with Ni and Au (ENIG process). Process details and layer thickness are not known. This plated thick film system was developed by Norbitech and NJ Innovation and it was interesting to see how an Al wire bond would behave under high temperature conditions. The used substrate was not designed for our test purpose. But, it was possible to use for a pure mechanical test of wire-bond strength before and after high temperature exposure.

Figure 16. Test substrate for wire bond evaluation tests.

Wedge-wedge aluminium wire-bonding with a 25  $\mu$ m diameter aluminium 1% silicon wire was used for testing. The loop height was 0.4 mm and the loop length was 1.5 mm. The samples were stored at 250 °C and 300 °C for up to 1000 hours.

#### 5.2 Results and discussion

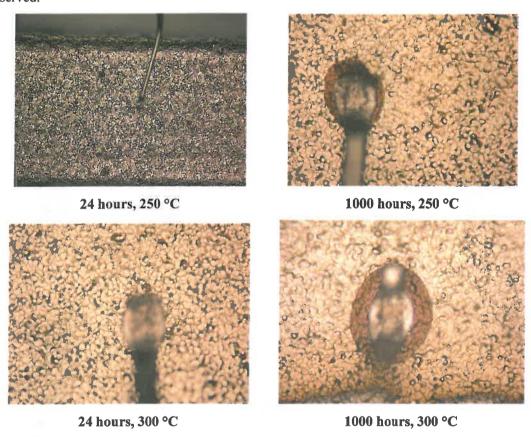

Microscopy – The samples were visually inspected in an optical microscope. In general, a change of colour was observed after thermal ageing, the gold surface was replaced by a darker surface. After 1000 hours of storage a change of colour was observed around the bonding site, a red area appears around the aluminium foot, see Figure 17. After 1000 hours at 300 °C. A colour change along the edges of the plated pads was observed.

Figure 17. Microscopy images of bonding site after high temperature storage (HTS).

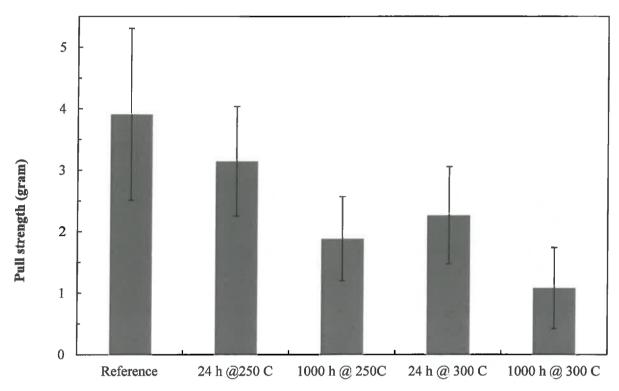

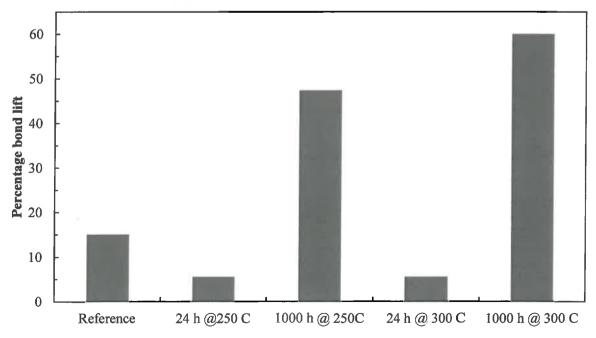

Pull testing – 20 bond-loops were pull tested for each ageing condition. The initial pull strength value was lower than expected, with an average value of 4 gram. (Similar systems usually show 8 – 10 gram and MIL-STD-883H require 2 g.) This was derived to originate from that the substrates had been stored for 10 months in office conditions (this should typically not affect the bondability). After high temperature storage the bond strength decreased, the decrease was larger for the samples stored at 300 °C than for the 250 °C samples, see Figure 18. Before ageing and after 24 hours storage the majority of bond failures were in the heel of the first bond. After 1000 hours of ageing 50 to 60 % of the failures were bond lift (i.e. the complete wire-bond is lifted off the surface), see Figure 19.

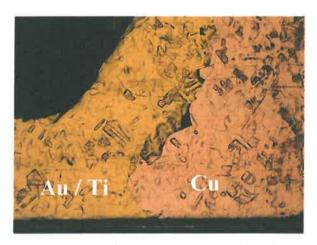

Cross-section – The bonds were cross-sectioned and inspected by optical microscopy, scanning electron microscopy (SEM) and by energy dispersive X-ray spectroscopy (EDS or EDX). The cross-section revealed a new intermetallic face at the interface between the wire bond and the pad on the substrate. Figure 20 show

a collection of SEM images at the heel. No Au was found in the bond interface but some Au remained just next to the bond interface.

Figure 18. Wire bond pull values.

Figure 19. Percentage bond lift.

Figure 20. SEM images of the bonding thread and the bonding with the substrate.

# 6 Encapsulation

Hermetic encapsulation, e.g. by potting materials or forming a solid enclosure with a cavity inside, around the electronic system is a common way to control the environment for the electronics. The cavity may either be evacuated or filled with a compatible material e.g. inert gas, gel or electronic liquid. Such enclosures require structural materials that are compliant with the materials inside the cavity, especially the circuit board. The package materials must also provide sufficient heat transfer capability to avoid high overtemperatures of the electronics inside that encapsulation.

There are several different packaging levels inside a complete package system that needs encapsulation materials. Examples of methods are; conformal coating, molding/ potting and sealants. These materials are typically polymers in various forms. PEEK, PEK and polyimide are common high temperature compatible examples. All polymers have a glass transition point,  $T_g$ , at which the material properties may change drastically. E.g. the CTE typically increases from tens of ppm/K to more than 100 ppm/K which cause a severe mismatch between materials and the strength of the polymer typically decrease significantly. Other crucial generic material properties of polymers that must but considered for reliable high temperature operation are decomposition temperature,  $T_d$ , and outgassing. Outgassing has proven to be a disingenuous issue that must be tested in in-situ like setups, such as in hermetic chambers together with the active electronic system. (Inside normal open ovens the gasses simply dissolve in the surrounding air and the potential long term effects are not captured.)

There are a vast number of suppliers of polymeric materials for encapsulation purposes. Some of the most interesting suppliers for high temperature compatible materials are; SCS, Victrex, DuPont, Greene Tweed and Lord. They all offer potential products for continuous operation above 200 °C. The materials may be applied in various ways; pored, painted, spray coated, vapor deposited, molded etc.

Structural materials – To build an enclosure around the electronic system materials with an excellent CTE match to an attached circuit board are crucial to design a robust and reliable system. The material must also have a high structural integrity and its porosity shall be very low. There are plenty of common ways and materials to build such structures. One may use the ceramic board itself as a structural component, building walls with a lid on top of it, or one may create a complete enclosure putting the circuit board inside it. Both options have advantages and disadvantages. Common high temperature compatible materials used for this include alumina (Al<sub>2</sub>O<sub>3</sub>), Kovar and common lead frame materials such as CuMo. AlSiC is a material with attractive thermo-mechanical properties which can be exploited for encapsulation purposes. It is typically used in electronic base plates (often in cold plates). Other novel materials include; nano and diamond composites which have extremely high thermal conductivity (>500 W/mK) combined with low CTE (<10 ppm/K).

Sealant - A high temperature compatible seal is typically soldered or brazed of with a metal solder, e.g. eutectic Au-Sn or Au-Ge, or welded. But polymers are also common, especially for lower temperature ranges. The scale factor of the enclosure requiring a seal sets stringent demands on the materials properties of the sealant. Mechanical strength, compliance and wetting properties with the structural materials used to form the cavity for which the seal shall maintain the hermeticity over time is crucial properties.

Conformal coating – Conformal coatings main purpose is to provide a protection layer on exposed surfaces of the electronics inside the enclosure. The coatings typically have high dielectric strength which makes the suitable to prevent shorts by arcing and surface migration of the materials beneath the coating. Another benefit from using a coating is that it immobilizes the atoms on the surface of the conducting traces which inhibit electromigration in the metal core region.

The case study investigated in this project request safe handling of transient but high voltage spikes in the magnitude order of 1000-1500 V. Since the SiC BJT is only about 330  $\mu m$  thick, i.e. the distance between collector and emitter, inert gases or vacuum won't do (they require at least 400  $\mu m$  isolation distances for

these voltage levels). I.e. a conformal coating is required at the board level near both the transistors and diodes.

Electronic liquid – Another way to provide a dielectric protection for short circuits is to fill the hermetic cavity with an electronic liquid, i.e. a dielectric liquid. In addition to the dielectric protection, an electronic liquid also improves the thermal performance of a device by allowing heat to escape from the front side of circuit board and components more effectively than gas or vacuum. Fluorinert liquids have been used for decades but due their harmful nature, both biological and their impact on the climate (global warming), novel liquids have emerged. Solvay, 3M, Exxon all offer interesting electronic liquids. Solexis Galden PFPE and Coolanol OS-59 are perhaps the most interesting high temperature alternatives with a high flash point and a stated operation temperature above 250 °C. Lots of uncertainties arise when using electronic liquids for longer periods of time at elevated temperatures; chemical compatibility with other materials in the packages, local charge build up, pressure build up, high temperature characteristics changes, decomposition etc.

## 6.1 Conformal coating

SCS Parylene HT (PHT) was chosen as the conformal coating for the surface of the ceramic circuit board with all components assembled. PHT has a dielectric strength of 200 V/ $\mu$ m, thus approximately 8  $\mu$ m is the minimum layer thickness to prevent electric breakdown for 1500 V, assuming a perfectly uniform and fault free material (as deposited). It can operate continuously at 350 °C (in air) and up to 450 °C for shorter periods. Coating may be structurally continuous for thicknesses ranging from < 1  $\mu$ m up to 75  $\mu$ m. Parylene HT is vapour phase deposited onto the surface which makes it ideal to get a uniform coating that cover all exposed surfaces closely without voids. It has been confirmed by the public domain that the coatings are exceptionally uniform and may cover complex structures with micron sized details in satisfactory way. A silane pre-treatment process is required to get good adhesion to Au surfaces. The adhesion to Au may be a major issue for the case study since the power module have Au as the top metallization. An experiment was planned to coat the final circuit board, with the Ni and Au, layers to qualify the coating for our design. But, since we never managed to plate this substrate, this experiment was never performed.

#### 6.2 Base plate

#### 6.2.1 Materials and methods

Silicon carbide reinforced aluminum, or AlSiC, is a rather novel material that combines both an attractive CTE match (< 6 ppm/K to 11 ppm/K) with a high thermal conductivity (180 W/mK to 200 W/mK). This makes it an attractive match with ceramic based electronic systems. AlSiC is typically produced through casting process. A porous SiC preform is filled with liquid Al in the casting process. This creates a component that is light weight with a pure Al surface. The Al surface may be cold spray coated with Cu, building a tens of microns thick Cu layer (e.g. for bond purposes). AlSiC is machinable and chemically stable with many common corrosive environments. AlSiC is very expensive compared to more common materials, but this is mainly due to the still low volumes requested today, according to the suppliers. Both the start-up cost, about kNOK 50-150 for tooling and design, and the part cost, NOK 500-5000, are high.

### 6.2.2 Results and discussion

Simulations of a simply supported stack with the  $Si_3N_4$  ceramic substrate attached with a Cu-Sn SLID bond to an AlSiC baseplate with a 150  $\mu$ m thick Cu surface layer was performed.

The simulations revealed relatively high plastic strains, (up to  $\sim 10$  %) in the Cu layer at the outmost corner of the Cu / AlSiC interface.

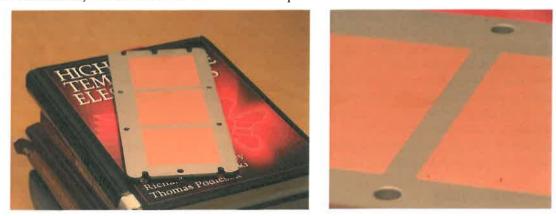

An AlSiC-10 base plate,  $220 \times 92 \text{ mm}^2$ , with three fields with a 150  $\mu m$  cold spray coated Cu layer on the surface, was acquired (Figure 21). The Si<sub>3</sub>N<sub>4</sub> circuit board was attached to the base plate with an adhesive (Duralco 4703). The assembly was put in an oven at 250 °C and stored there for 2700 hours (in air).

No faults or unexpected behaviour of the AlSiC base plate was observed. Cracks or delamination, suggested by the simulations, was not observed on the tested samples.

Figure 21. AlSiC base plate with 150 µm Cu top metallization.

The results regarding the AlSiC base plate are discussed in more detail in section 7.

# 6.3 Electronic liquid

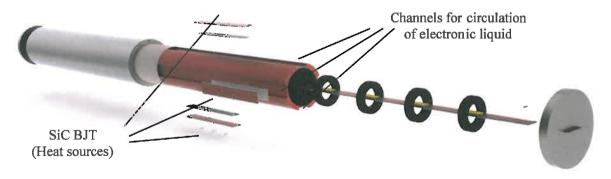

A potentially attractive solution to improve the thermal performance of an electronic device that dissipates heat with high energy density (the SiC BJT in the case study dissipates ~1.6 MW/m²) is cooling from both sides of the active chip. Electronic liquids provide a means to achieve this. High heat transfer coefficients may be achieved by using a liquid (up to 1000 W/m²K for convection and up to 20000 W/m²K by a phase change processes).

## 6.3.1 Results and discussion

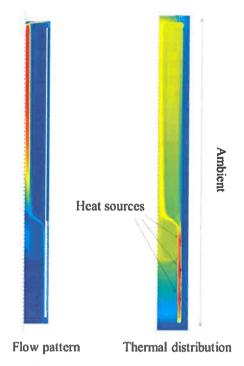

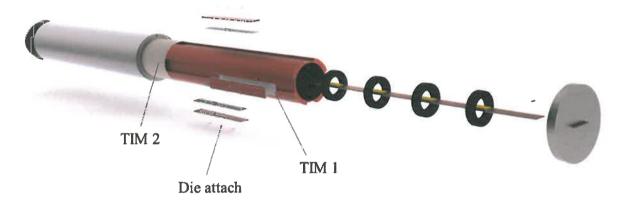

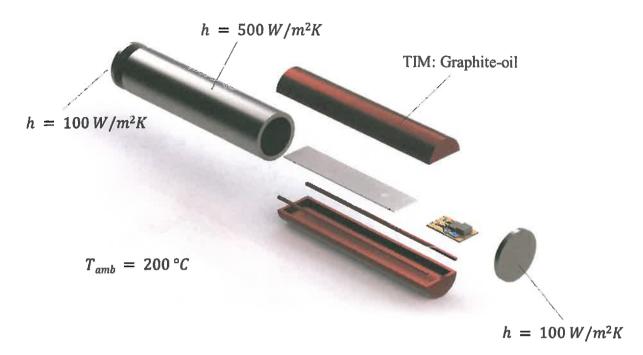

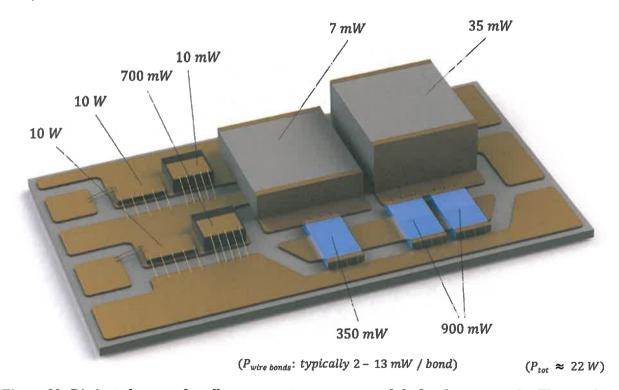

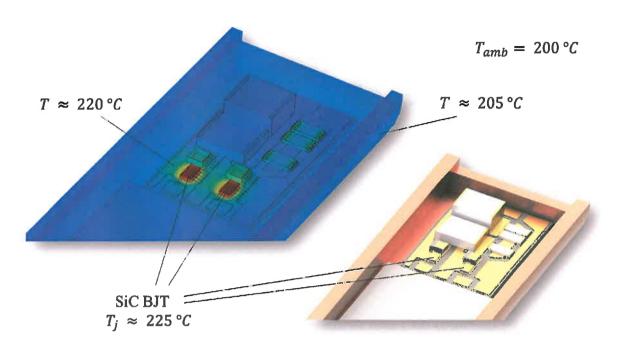

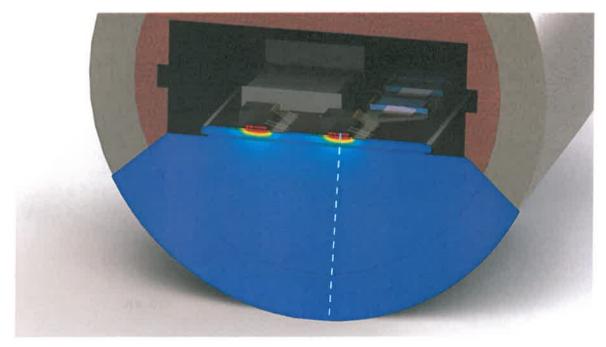

Simulations on early concepts for the case study (Figure 22 and Figure 23) revealed that the additional need for cooling was limited for the suggested system, since the primary heat path, through die / die attach / substrate / TIM / base plate / TIM, was found to be very efficient with limited over-temperatures. Since the additional cooling performance was limited, and the added complexity by using an electronic liquid, it was not used in the final concept. For future concepts it may be reconsidered, especiall if the energy density increases significantly.

Figure 22. Illustration (exploded view) of an early concept. The concept contains integrated channels for circulation of electronic liquid flowing past the SiC BJT.

Figure 23. Flow pattern and thermal distribution for an early concept with liquid cooling (circulation of an electronic liquid by natural convection). The dashed lines indicate the symmetry axis for the 2D axisymmetric model.

#### 7 Thermal interface materials

Different high temperature adhesives and metallic bonds were investigated regarding application as thermal interface materials (TIMs). TIMs are materials used to minimize the thermal contact resistance in the interfaces between the different layers/ levels in a package. In addition, it is sometimes used as an adhesive/ joint to secure components to one another. Important characteristics are low thermal bulk conductivity and low effective thermal resistance, i.e. the sum of the resistance due to thermal conductivity of the TIM and contact/ interface resistance between the TIM and the two contacting surfaces. The effective thermal resistance is among other things dependent of the thickness of the TIM and the actual area in which the TIM and contacting layers have mechanical contact. An overview of the different interfaces requiring TIMs in this project is given in Figure 24. Die attach is used to fix components, e.g. transistor, resistor and capacitor, to the substrate. It needs to have low thermal resistance, and in some cases it needs to be electrical conductive. The different die attach materials investigated in this project is summarized in section 4. One TIM was used to fix the substrate mechanically to a support structure (avoid screws/clamps which are known to generate unpredictable behavior (reliability) in similar systems), and ensure low thermal resistance. A second TIM was applied to minimize thermal resistance between support structure and external housing.

Figure 24. A schematic overview, identifying the main interfaces where a thermal interface material (TIM) is required.

#### 7.1 High temperature Adhesives

In an adhesive used for thermal management, the mechanical strength comes from the matrix, while the particles/ material base provide the chief part of the effective thermal conductivity. Advantages with adhesives or filled polymers used as thermal interface materials (TIMs) include that they are easy to handle (relatively), conforms to surface irregularity before cure, have a low elastic modulus and excellent resistance to most chemicals and solvents. They can also easily be adjusted to the size of the mounting surfaces. Disadvantages include that curing is required, thermal conductivity is low compared to that of pure metals and delamination and adhesion (specially to Au) can be a problem in addition to thermal degradation. Delamination can be a result of the coefficient of thermal expansion (CTE) mismatch between the polymer and the fillers. This will create local stress inside the filled adhesive, possibly leading to cracks and delamination.

## 7.1.1 Materials and Methods

An overview of the different high temperature adhesives investigated in this project can be found in Table 4. Note that Au-Sn and Cu-Sn SLID are included for comparison.

The two most investigated adhesives were Resbond 931 and Duralco 4703. Resbond 931 is a graphite filled silica with good thermal conductivity and a high degradation temperature which is reported to give interface

thicknesses down to 100 µm. The degradation or decomposition temperature are important parameters since the decomposition of a high temperature adhesive usually only involve decomposition of the polymer. This can potentially change the properties and reduce the reliability of the adhesive, since the polymer provides the mechanical strength. Outgassing, which is closely connected to degradation, is also an important parameter. The outgassing of Resbond 931 is relatively low at 300 °C compared to the intended operation temperature of the case study (200 to 250 °C).

Duralco 4703 is an epoxy filled with Al<sub>2</sub>O<sub>3</sub> powder. It offers high temperature stability (degradation temperature of 330 °C), has excellent resistance to most chemicals and is easily handled. The interface thickness of a Duralco 4703 bond can be made very thin, giving low effective thermal resistance.

An overview of the different substrates and chips/bricks used to test the different adhesives can be found in Table 5. Before assembly, the substrates and chips/bricks were cleaned with acetone, isopropanol and dried with nitrogen. All the tested adhesives were mixed, applied and cured according to the data sheets provided by the different suppliers.

After assembly the samples were characterized with shear testing (in a Dage 2400A or NordsonDage 4000plus) and by optical microscopy. Some samples were cross-sectioned and inspected by optical microscopy.

Selected samples were stored at high temperature (HTS), at 250 °C, for 2600 hours. The samples were visually inspected once a week to check for obvious degradation, such as catastrophic mechanical failure by detached substrates from the base plate.

Table 4. Overview of different thermal interface materials investigated.

| Name          | Material<br>base                                 | Effective<br>thermal<br>conductivity | Degradation<br>temperature<br>(°C) | Outgassing @ 300 °C | Expected final layer thickness | Estimated thermal resistance <sup>3</sup> |

|---------------|--------------------------------------------------|--------------------------------------|------------------------------------|---------------------|--------------------------------|-------------------------------------------|

|               |                                                  | (W/m·K)                              | ( -)                               |                     | (µm)                           | (mm <sup>2</sup> ·K/W)                    |

| Au-Sn SLID    | Gold and tin                                     | 60                                   | T <sub>m</sub> : 522               | ===                 | ~10                            | ~0.17                                     |

| Cu-Sn SLID    | Copper and tin                                   | 104                                  | T <sub>m</sub> : 676               | -                   | <10                            | <0.10                                     |

| Duralco 4703  | Epoxy with Al <sub>2</sub> O <sub>3</sub> powder | 2,55                                 | 330                                | 0.33%               | ~50                            | ~20                                       |

| Epo-tek 353ND | Ероху                                            | 0.10-0.15                            | 412                                | 0.87%               | ~4-6                           | ~40                                       |

| Resbond 906   | Silicate with magnesia                           | 5.6                                  | 1650                               | Low                 | ~100                           | ~17.9                                     |

| Resbond 931   | Silicate with graphite                           | 8                                    | 3000                               | -                   | ~100                           | ~12.5                                     |

| Resbond 954   | Silicate with stainless                          | >2                                   | 1200                               | Low                 | ~100                           | ~50                                       |

| Staystik® 581 | Silver                                           | >3                                   | 300                                | Low                 | 38                             | 12.7                                      |

Table 5. Overview of the different substrates and chips used for the different adhesives tested. The measured shear strength is also included where applicable.

| Substrate                                                                    | Chip/ brick                                                       | Adhesive                                                     | Shear strength                                                    |

|------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------|

|                                                                              |                                                                   |                                                              | (MPa)                                                             |

| Cu / Ni plated<br>Si <sub>3</sub> N <sub>4</sub><br>(6 x 6 mm <sup>2</sup> ) | Au plated Cu (3 x 3 mm <sup>2</sup> )                             | Resbond 906<br>Resbond 931<br>Durabond 954                   | NA<br>NA<br>NA                                                    |

| Cu / Ni plated<br>Si <sub>3</sub> N <sub>4</sub><br>(6 x 6 mm <sup>2</sup> ) | Cu<br>(3 x 3 mm <sup>2</sup> )                                    | Resbond 906<br>Resbond 931                                   | 1.3<br>3.4                                                        |

| Cu plated Si <sub>3</sub> N <sub>4</sub> (6 x 6 mm <sup>2</sup> )            | Cu (3 x 3 mm <sup>2</sup> )                                       | Resbond 931<br>Epo-tek 353ND<br>Staystik 581<br>Duralco 4703 | 6-7<br>7<br>NA<br>29                                              |

| Cu plated Si <sub>3</sub> N <sub>4</sub> (6 x 6 mm <sup>2</sup> )            | Ceramic<br>resistor<br>(Vishay PHT<br>2010)                       | Duralco 4703                                                 | 21                                                                |

| AlSiC baseplate (see Figure 25)                                              | Cu plated Si <sub>3</sub> N <sub>4</sub> (6 x 6 mm <sup>2</sup> ) | Duralco 4703                                                 | NA: Not possible to shear of the substrate due to large bond area |

Table 6. Overview of the TIM systems exposed for HTS. The measured shear strength is also included where applicable.

| Substrate                                                         | Chip/ brick                                                       | Adhesive     | Shear strength |  |

|-------------------------------------------------------------------|-------------------------------------------------------------------|--------------|----------------|--|

|                                                                   |                                                                   |              | (MPa)          |  |

| Cu plated Si <sub>3</sub> N <sub>4</sub> (6 x 6 mm <sup>2</sup> ) | Ceramic resistor                                                  | Duralco 4703 | 4              |  |

| AlSiC baseplate                                                   | Cu plated Si <sub>3</sub> N <sub>4</sub> (6 x 6 mm <sup>2</sup> ) | Duralco 4703 | -              |  |

Figure 25.  $Si_3N_4$  substrates glued to an AlSiC baseplate with Duralco 4703. Two of the substrates contains three (six in total) Vishay PHT 2010 resistors glued with the same Duralco 4703.

#### 7.1.2 Results and discussion

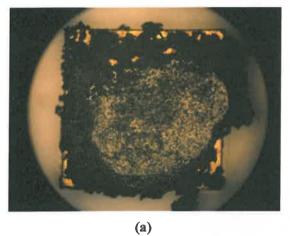

All samples glued with Resbond 906, Resbond 954 and Staystik 581 failed before shear testing or cross-sectioning. The main reason for this was poor adhesion. A typical fracture surface is shown in Figure 26. This image is also representative for the other fractures.

Figure 26. Fracture surfaces of samples bonded with Resbond 954.

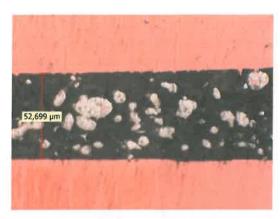

After some process optimization, acceptable adhesion was achieved with Resbond 931,  $\sim$ 6 MPa. However, the interface was quite thick,  $\sim$ 200 $\mu$ m, and the adhesive was very difficult to work with.